1. Memahami karakteristik Programmable Array Logic

2. Membuat rangkaian dari Programmable Array Logic

3. Menjalankan dan menganalisa rangkaian Programmable Array Logic

2.Alat Dan Bahan

1.Gerbang OR

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

2.Gerbang AND

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali.

3.Gerbang NOTGerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan (kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“) di atas Variabel Inputnya.

4.LED yellow

Komponen elektronika yang dapat memancarkan cahaya monokromatik ketika diberikan tegangan maju. LED merupakan keluarga Dioda yang terbuat dari bahan semikonduktor. Warna-warna Cahaya yang dipancarkan oleh LED tergantung pada jenis bahan semikonduktor yang dipergunakannya. LED juga dapat memancarkan sinar inframerah yang tidak tampak oleh mata seperti yang sering kita jumpai pada Remote Control TV ataupun Remote Control perangkat elektronik lainnya.

5.Resistor

Resistor merupakan komponen elektronika yang berguna untuk menghambat aliran arus listrik sehingga tidak terjadi short circuit. mempunyai resistansi yang berbeda beda sesuai kebutuhan.

6. IC D-FLip Flop

D Flip-flop merupakan salah satu jenis Flip-flop yang dibangun dengan menggunakan Flip-flop RS. Perbedaan dengan Flip-flop RS terletak pada inputan R, pada D Flip-flop inputan R terlebih dahulu diberi gerbang NOT. maka setiap masukan ke D FF ini akan memberi keadaan yang berbeda pada input RS, dengan demikian hanya terdapat 2 keadaan “SET” dan “RESET” S=0 dan R=1 atau S=1 dan R=0, jadi dapat disi. Berikut adalah gambar dari symbol dan data sheet D Flip – flop.

[kembali]

3.Dasar Teori

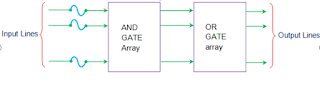

Programmable Array Logic (PAL) adalah jenis Programmable Logic Device (PLD) yang digunakan untuk mewujudkan fungsi logis tertentu. PAL terdiri dari array gerbang AND diikuti oleh array gerbang OR seperti yang ditunjukkan oleh Gambar 1. Namun perlu dicatat bahwa di sini hanya array gerbang AND yang dapat diprogram tidak seperti array gerbang OR yang memiliki logika tetap. Ini karena di sini input dimasukkan ke gerbang AND melalui sekering (ditunjukkan dengan warna biru), yang bertindak sebagai tautan yang dapat diprogram. Programmable-AND dan fixed-OR struktur PAL membuatnya kurang fleksibel dari sudut pandang pemrograman bila dibandingkan dengan Programmable Logic Arrays (PLA). Namun karena alasan yang sama PAL lebih murah daripada PLA.

|

| Gambar 1. Programmable Array Logic(PAL) |

gambar 2 menunjukkan struktur internal PAL dengan input m dan output n. Setiap jalur input ditunjukkan melewati buffer dan / atau inverter. Semua input ini terhubung masing-masing dan setiap gerbang AND yang ada di PAL.

Lebih lanjut, matriks koneksi ini dapat diprogram (kotak merah pada Gambar 2) yang memungkinkan pengguna untuk memutuskan koneksi antara jalur input dan gerbang AND. Ini berarti bahwa seseorang harus menghubungkan setiap jalur input ke gerbang AND tunggal atau ganda, tergantung pada logikanya. Ini menyebabkan seseorang menyadari fungsionalitas 'dan' logis di antara jalur input. Lebih lanjut, output dari array gerbang AND dimasukkan sebagai input ke gerbang OR melalui koneksi kabel (ditunjukkan oleh kotak biru pada Gambar 2), yang diperbaiki dan karenanya tidak dapat diubah. Terlebih lagi harus dicatat bahwa output dari setiap gerbang AND tidak diumpankan ke setiap gerbang OR. Misalnya, gerbang OR 1 (O 1 ) memiliki banyak input termasuk output dari gerbang AND 1 (A 1 ), gerbang AND 2 (A 2 ) dan gerbang AND p (A p ).

Namun gerbang OR n (O n ) hanya memiliki dua input yang merupakan output dari gerbang AND A 1 dan A p . Ketika koneksi-koneksi ini diperbaiki, kita harus memperhatikan ketika membangun koneksi untuk mewujudkan fungsionalitas logis 'atau' dari istilah-istilah produk yang diperoleh sebagai output dari AND gate array.

|

| Gambar 2. Struktur dalam dari Programmable Array Logic |

Akhirnya ada n garis output dari array gerbang OR yang menghasilkan n output PAL mewujudkan logika yang diperlukan dalam bentuk jumlah produk (SOP). PAL yang ditunjukkan pada Gambar 2 dapat diatasi sebagai m-input, p-product-term, n-output PAL. Namun perlu dicatat bahwa jumlah input, gerbang AND dan gerbang OR yang ada di PAL semuanya independen yaitu satu PAL dapat memiliki 3 input, 8 gerbang AND dan 4 output (dan dengan demikian 4 gerbang OR).

Semua PAL dapat diprogram secara elektrik menggunakan file bit melalui pemrogram perangkat. Pengumpan perangkat lebih lanjut dan pemrogram geng dapat digunakan untuk memprogram lebih dari satu PAL . Bahasa pemrograman yang umum digunakan termasuk PAL assembler (PALASM), Compiler for Universal Programmable Logic (CUPL) dan Advanced Boolean Expression Language (ABEL).

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y

|

| Gambar 3. Rangkaian dari PAL |

AND array telah diprogram tetapi harus bekerja dengan array OR tetap sesuai kebutuhan. Jalur yang diinginkan akan terhubung dalam PLD.

Keuntungan PAL:

· Sangat efisien

· Biaya produksi rendah dibandingkan dengan PLA

· Sangat aman

· Keandalan Tinggi

· Daya rendah diperlukan untuk bekerja.

· Lebih fleksibel untuk desain.

Fleksibilitas perangkat PAL bisa ditingkatkan dengan memiliki konfigurasi logika output yang berbeda termasuk ketersediaan keduanya OR (juga disebut active HIGH) dan NOR (juga disebut active LOW) output dan bidirectional pin yang dapat bertindak baik sebagai input dan output, setelah flip-flop clock pada output untuk memberikan apa yang disebut terdaftar output. Fitur-fitur ini memungkinkan perangkat untuk digunakan dalam berbagai aplikasi yang lebih luas daripada yang seharusnya mungkin dengan perangkat dengan alokasi input dan output tetap. Versi PAL yang diprogram topeng dikenal sebagai perangkat HAL (Hard Array Logic). Perangkat HAL kompatibel pin-to-pin dengan PAL-nya rekanan.

|

| Gambar 4. a,b,c dan d merupakan karnaugh map |

Menjelaskan struktur PAL (diprogram DAN gerbang diikuti oleh gerbang OR tetap).

Contoh: Sadarilah fungsi yang diberikan dengan menggunakan PAL:

Segala bentuk dari bentuk jumlah produk (SOP) atau produk jumlah (POS) dapat digunakan untuk realisasi fungsi boolean.Ada tiga input A, B, C dan tiga fungsi X, Y, Z. Menggunakan istilah penjumlahan produk (SOP) untuk menyatakan fungsi yang diberikan sebagai berikut: -

Tabel Kebenaran berikut akan membantu dalam memahami fungsi pada sejumlah input:

|

| Gambar 5. Tabel Kebenaran |

Arsitektur PAL

|

| Gambar 6. Programmed PAL Device |

Sistem Penomoran PAL

Sistem penomoran PAL standar menggunakan penunjukan alfanumerik yang terdiri dari angka dua digitmenunjukkan jumlah input diikuti oleh surat yang menceritakan tentang arsitektur / jenis output logika. tabel 8 dibawah memberikan interpretasi penunjukan huruf yang berbeda yang digunakan. Nomor lain mengikuti

|

| Gambar 7.Generalized PAL device |

|

| Gambar 8. Programmability of inputs in a PAL device. |

|

| Gambar 9. Output logic arrangements in a PAL device |

|

| Gambar 10. Tabel Sistem penomoran |

4.Percobaan

A. Percobaan Rangkaian 1

|

| Gambar 11.Saat input logika 000 |

-Pada saat input dari logicstate berlogika '0' maka pada inverter akan berlogika 1 lalu pada kaki gerbang AND 1 akan berlogika '1' dan '0' sehingga pada output gerbangnya akan berlogika '0' lalu akan menuju ke gerbang OR karena input gerbang OR '0' maka output dari gerbang OR akan '0' sehingga led menjadi mati

-Pada Gerbang AND 3 karena input dari gerbang AND '1' dan '1' maka output nya akan berlogika 1 sedangkan pada gerbang AND 4 berlogika '1' dan '0' maka outputnya akan menjadi '0' sehingga LED akan menyala redup.

-pada LED 3 sama kondisinya seperti LED 1

|

| Gambar 12.Saat input logika 111 |

-Pada saat input dari logicstate berlogika '1' maka pada inverter akan berlogika 0 lalu pada kaki gerbang AND 1 akan berlogika '0' dan '1' maka output nya akan berlogika '0', pada gerbang AND 2 akan berlogika '1' sehingga pada output gerbangnya akan berlogika '1' lalu akan menuju ke gerbang OR karena input gerbang OR '1' maka output dari gerbang OR akan '1' sehingga led menjadi hidup

-Pada Gerbang AND 3 karena input dari gerbang AND '0' dan '0' maka output nya akan berlogika '0' sedangkan pada gerbang AND 4 berlogika '1' dan '0' maka outputnya akan menjadi '0' sehingga LED tidak menyala.

-pada LED 3 sama kondisinya seperti LED 1

|

| Gambar 13. Saat input logika 110 |

-Pada saat input dari logicstate berlogika '1' maka pada inverter akan berlogika 0 lalu pada kaki gerbang AND 1 akan berlogika '0' dan '1' maka output nya akan berlogika '0', pada gerbang AND 2 akan berlogika '1' dan '0' sehingga pada output gerbangnya akan berlogika '0' lalu akan menuju ke gerbang OR karena input gerbang OR '0' maka output dari gerbang OR akan '0' sehingga LED tidak menyala

-Pada Gerbang AND 3 karena input dari gerbang AND '0' dan '0' maka output nya akan berlogika '0' sedangkan pada gerbang AND 4 berlogika '0' dan '0' maka outputnya akan menjadi '0' sehingga LED tidak menyala.

-pada LED 3 saat input inverter 0 maka pada gerbang AND 5 akan berlogika '0' dan 1 sehingga outputnya akan '0' pada gerbang AND 6 akan berlogika '1' dan '0' sehingga output akan berlogika 0 dan pada gerbang AND 7 input berlogika '1','0','0' sehingga outputnya berlogika 0 dan LED tidak menyala.

B. Percobaan Rangkaian 2

Gambar 14. Programmability of inputs in a PAL device.

Prinsip Kerja :Saat rangkaian inverter 1,2,3,dan 4 berlogika 1 maka pada inverter akan berlogika 0 lalu menuju kaki AND karena kaki AND berlogika 1 sehingga menyebabkan output dari AND berlogika 1.

pada saat rangkaian inverter 1,2,3,dan 4 berlogika 0 maka pada inverter berlogika 1 lalu menuju kaki dari AND karena kaki and berlogika 0 maka menyebabkan output dari AND berlogika 0

C. Percobaan Rangkaian 3

|

| Gambar 15. rangkaian 2 Generalized PAL device |

pada saat rangkaian berlogika 1 arus akan masuk ke inverter sehingga akan berlogika 0 karena kaki dari AND berlogika 1 sehingga menyebakan output dari AND berlogika 1 lalu diteruskan menuju Gerbang OR karena gerbang OR berlogika 1 maka outputnya akan berlogika 1 lalu menuju inverter dirubah menjadi 0 sehingga outputnya berlogika 0

|

| Gambar 16. rangkaian arrangements in a PAL device |

pada saat rangkaian berlogika 0 maka output dari or akan berlogika 0 lalu menuju D dari D-flipflop lalu keluara dari D flipflop adalah logika 0 sehingga output dari and berlogika 0 lalu dilanjutkan ke buffer sehingga outputnya nol, daru output AND dilanjutkan menuju kaki inverter dan AND sehingga output yang didapatkan pada gerbang AND berlogika 0.

pada saat rangkaian berlogika 1 maka output dari or akan berlogika 1 lalu menuju D dari D-flipflop lalu keluara dari D flipflop adalah logika 1 sehingga output dari and berlogika 1 lalu dilanjutkan ke buffer sehingga outputnya 1, dari output AND dilanjutkan me

nuju kaki inverter dan AND sehingga output yang didapatkan pada gerbang AND berlogika 1.

nuju kaki inverter dan AND sehingga output yang didapatkan pada gerbang AND berlogika 1.

Sistem penomoran PAL standar menggunakan penunjukan alfanumerik yang terdiri dari angka dua digitmenunjukkan jumlah input diikuti oleh surat yang menceritakan tentang arsitektur / jenis output logika.huruf menunjukkan jumlah output. Dalam hal perangkat PAL menawarkan kombinasi yang berbedajenis keluaran logika, angka paling kanan menunjukkan jumlah jenis keluaran yang tersirat olehsurat yang digunakan dalam penunjukan. Misalnya, perangkat PAL yang ditunjuk PAL-16L8 akan memiliki 16 inputdan delapan output RENDAH aktif. Perangkat PAL lain yang ditunjuk PAL-16R4 memiliki 16 input dan empatoutput terdaftar. Juga, jumlah input seperti yang diberikan oleh penunjukan nomor termasuk berdedikasiinput, input yang dapat diprogram pengguna yang dapat diakses dari pin I / O kombinasi dan input umpan balik apa pun

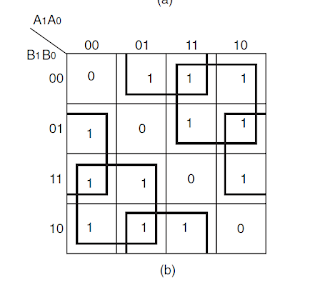

Dari tabel fungsi yang diberikan, kita dapat menulis ekspresi Boolean untuk empat output sebagai berikut:

|

| Gambar 18 Rumus Ekspresi Boolean dari rangkaian 5 |

Peta Karnaugh untuk empat keluaran P, Q, R dan S masing-masing diperlihatkan dalam Gambar 9.21 (a) hingga (d). Ituekspresi Boolean yang diperkecil diberikan oleh persamaan :

|

| Gamba 19. tabel kebenaran |

Langkah selanjutnya adalah memilih perangkat PAL Karena ada empat fungsi output, perlu perangkat PAL dengan setidaknya empat OR gerbang di output. Karena masing-masing gerbang OR harus dipasangkan dengan kabeluntuk hanya sebagian dari array DAN diprogram, dan juga karena salah satu fungsi output memiliki empat istilah produk, kita akan membutuhkan array AND 16 gerbang AND. Karena ada empat variabel input, perlu setiap gerbang AND dalam array untuk memiliki delapan input untuk memenuhi empat variabel dan komplemennya.Singkatnya, kami memilih perangkat PAL yang memiliki delapan input, 16 gerbang AND di diprogram ANDarray dan empat gerbang OR pada output. Setiap gerbang OR memiliki empat input.Gambar diats menunjukkan arsitektur perangkat PAL yang diprogram. Kita dapat melihat bahwa output Phanya memiliki tiga syarat produk. Input keempat ke gerbang OR yang relevan perlu diterapkan logika '0'memasukkan. Ini dicapai dengan mengumpankan input gerbang AND yang sesuai dengan keempat variabeldan pelengkap mereka. Logika 0, di mana pun diperlukan, diimplementasikan dengan cara yang sama. Perhatikan bahwa,dalam perangkat PAL yang diprogram , interkoneksi yang tidak terprogram yang ditunjukkan oleh tanda silang(× adalah koneksi 'buat')

5.Video

Rangkaian 1

Rangkaian 2

Rangkaian 3

Rangkaian 4

Rangkaian 5

6.Link Download

Download Video 1 disini

Download Video 2 disini

Download Video 3 disini

Download Video 4 disini

Download Video 5 disini

Download HTML disini

Download Simulasi Rangkaian 1 disini

Download Simulasi Rangkaian 2 disini

Download Simulasi Rangkaian 3 disini

Download Simulasi Rangkaian 4 disini

Download Simulasi Rangkaian 5 disini

Download Data Sheet PAL disini

Download Data Sheet D-Flip FlopL disini

Download Data Sheet Inverter (7414) disini

Download Data Sheet AND (IC7408) disini

Download Data Sheet 74125) disini

[kembali]

No comments:

Post a Comment